-

- Neubau

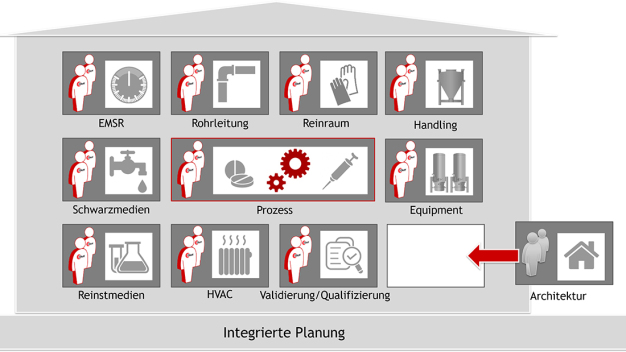

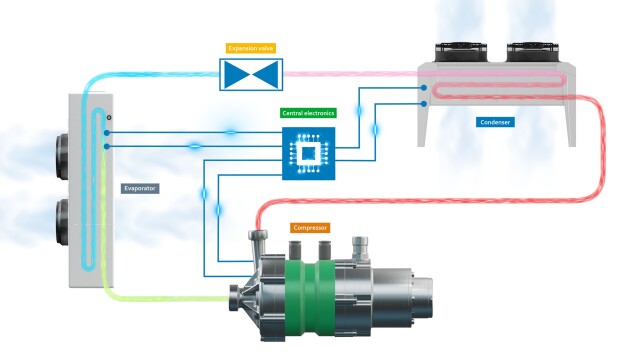

70 Mitarbeitende arbeiten interdisziplinär an der Entwicklung und Herstellung von kompakten und energieeffizienten Turbo-Kompressoren – vom Prototyp bis zur Serienreife

ebm-papst eröffnet HighSpeed-Technikum

Die ebm papst Gruppe, weltweit führender Anbieter von Ventilatoren und Motoren, hat heute in Mulfingen ihr neues HighSpeed-Technikum offiziell in Betrieb genommen. Im Beisein des Ministerpräsidenten Winfried Kretschmann, Harald Ebner, MdB, Catherine Kern, MdL, Ian Schölzel, Landrat des Hohenlohek…