- Elektronik (Wafer, Halbleiter, Mikrochips,...)

Imec demonstriert funktionale monolithische CFET-Bauelemente mit gestackten unteren und oberen Kontakten

Diese Woche präsentiert imec, ein weltweit führendes Forschungs- und Innovationszentrum für Nanoelektronik und digitale Technologien, auf dem 2024 IEEE Symposium über VLSI-Technologie und -Schaltungen (2024 VLSI) erstmals elektrisch funktionsfähige CMOS-CFET- Komponenten mit gestackten unteren und oberen Source/Drain-Kontakten. Während die Ergebnisse mit beiden Kontakten auf der Vorderseite erzielt wurden, beweist imec auch, dass es möglich ist, die Ausbildung des unteren Kontakts auf die Rückseite des Wafers zu verlagern und so die Wahrscheinlichkeit des "Überlebens" des oberen Bauteils von 11% auf 79% zu erhöhen.

Die Logik-Technologie-Roadmap von Imec sieht die Einführung komplementärer FETs (CFETs) in A7-Node-Bauteilarchitekturen vor. In Kombination mit fortschrittlichen Routing-Techniken versprechen CFETs eine Reduzierung der Standard-Zellspurhöhen von 5T auf 4T und sogar noch weniger, ohne dass die Leistungsfähigkeit darunter leidet. Unter den verschiedenen Ansätzen zur Integration von vertikal gestapelten n- und pMOS-Strukturen gilt die monolithische Integration als der am wenigsten disruptive Ansatz im Vergleich zu den bestehenden nanosheetartigen Prozessabläufen.

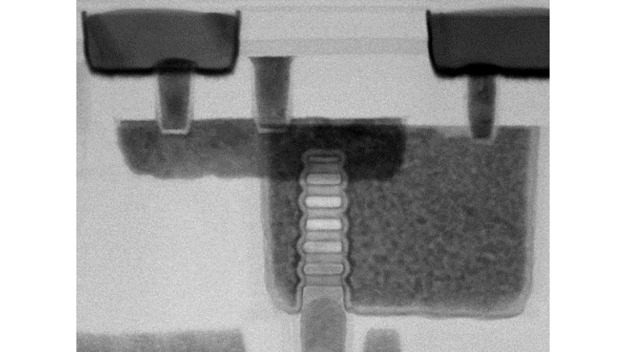

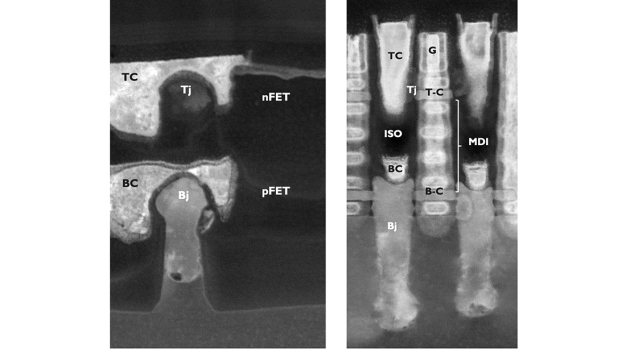

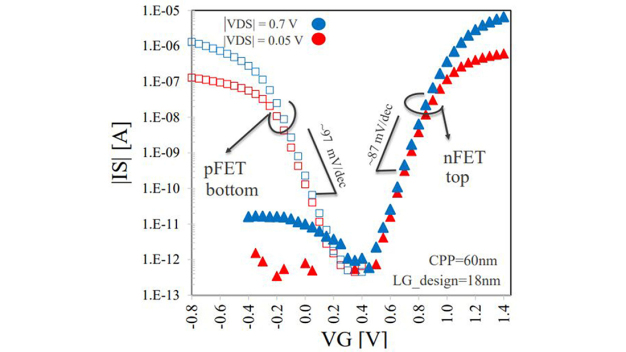

Auf dem VLSI-Symposium 2024 demonstriert imec erstmals funktionale monolithische CMOS-CFET- Bausteine mit übereinander angeordneten oberen und unteren Kontakten. Die CFETs wurden mit einer Gate-Länge von 18nm, einem Gate-Abstand von 60nm und einem vertikalen Abstand von 50nm zwischen n- und p-Bauteilen integriert. Die elektrische Funktionalität wurde an einem Versuchsträger mit nFET- und pFET-Bauelementen demonstriert, die ein gemeinsames Gate verwenden und deren obere und untere Kontakte von der Vorderseite her verbunden sind.

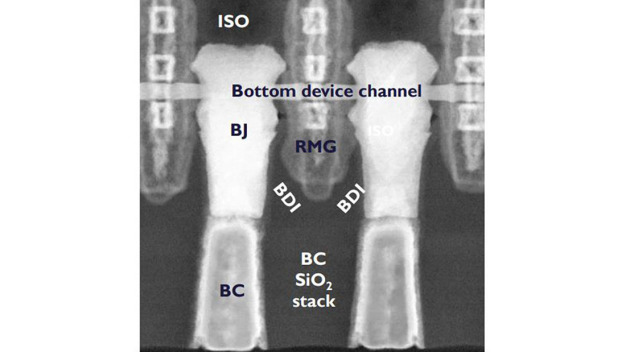

Der vorgeschlagene Prozessablauf umfasst zwei CFET-spezifische Module: die mittlere dielektrische Isolation (MDI) und die gestapelten unteren und oberen Kontakte.

MDI ist ein von imec entwickeltes Modul zur Isolierung des oberen und unteren Gates und zur Unterscheidung der Schwellenspannungseinstellungen zwischen n- und p-Bauelementen. Das MDI-Modul basiert auf einer Modifizierung des 'aktiven' mehrlagigen Si/SiGe-Stapels der CFETs und ermöglicht die Co-Integration des inneren Spacers - einer nanosheet-spezifischen Eigenschaft, die das Gate von Source/Drain isoliert. Naoto Horiguchi, Direktor CMOS-Bautechnologie bei imec: "Wir haben die besten Ergebnisse in Bezug auf die Prozesskontrolle mit einem MDI-First-Ansatz erzielt, d.h. vor der Source/Drain-Rekonstruktion - dem Schritt, bei dem die Nanosheets und das MDI 'gespalten' werden, um Zugang zu den Kanalseitenwänden zu erhalten und die Source/Drain-Epi zu starten. Ein innovatives Source/Drain-Recess-Ätzverfahren mit 'In-Situ-Capping' ermöglicht MDI-first, indem es die Gate-Hardmaske/Gate-Spacer während des Source/Drain-Recesses schützt."

Ein zweites kritisches Modul ist die Gestaltung von gestapelten Source/Drain-"Bottom"- und "Top"-Kontakten, die durch eine dielektrische Isolierung vertikal getrennt sind. Die wichtigsten Schritte sind das Füllen des unteren Kontakts mit Metall und das Rückätzen sowie das anschließende Füllen mit Dielektrikum und das Rückätzen - alles auf demselben engen Raum, der für den MDI- Stack zur Verfügung steht.

Naoto Horiguchi: "Bei der Entwicklung der unteren Kontakte von der Vorderseite aus sind wir auf mehrere Hindernisse gestoßen, die sich auf den Kontaktwiderstand auf der Unterseite auswirken und das Prozessfenster für die Bildung der Source/Drain-Bauteile auf der Oberseite einschränken. Im Rahmen der 2024 VLSI zeigen wir, dass es möglich ist, die Bildung der unteren Kontakte auf die Rückseite des Wafers zu verlagern, trotz zusätzlicher Prozessschritte im Zusammenhang mit dem Wafer-Bonding und der Ausdünnung. Die "Überlebensrate" der Top Devices stieg von 11% auf 79%, was die Bildung des unteren Kontakts auf der Rückseite zu einer attraktiven Option für die Industrie macht. Derzeit laufen Forschungen, um den optimalen Pfad für die Kontaktbildung zu finden."

IMEC Belgium

3001 Leuven

Belgien