-

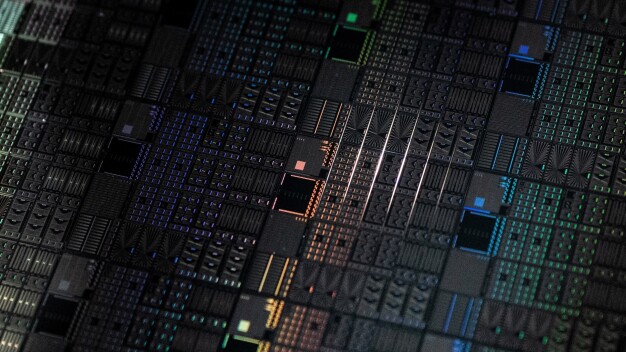

- Electronics (wafers, semiconductors, microchips,...)

New partnership enables an innovative network together with academia and industry partners to strengthen digital sovereignty in Europe

Baden-Württemberg attracts imec to lead development of chiplet-based technology for automotive applications

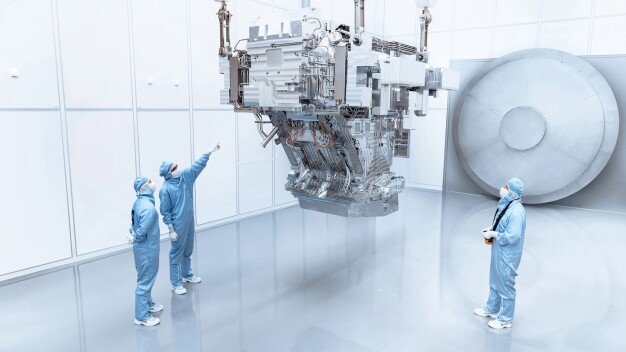

Imec, a world-leading research and innovation hub in nanoelectronics and digital technologies, and the State Government of Baden-Württemberg, Germany, today announced, at the Hannover Trade Fair, the launch of the Advanced Chip Design Accelerator (ACDA). The new imec competence center in Baden-Wür…