- Elektronik (Wafer, Halbleiter, Mikrochips,...)

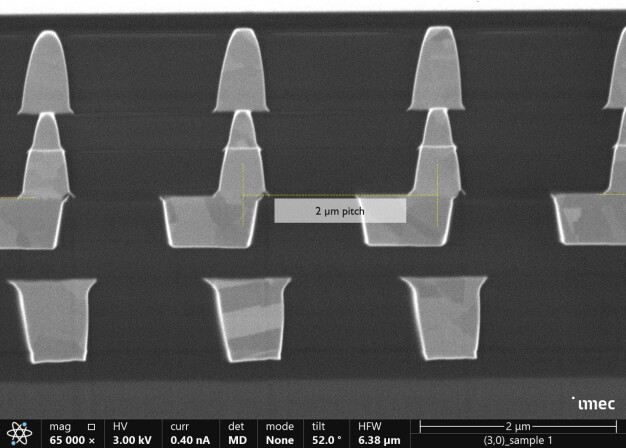

Imec demonstriert Die-to-Wafer-Hybridbonden mit einem Cu-Interconnect-Pad-Pitch von 2µm

Verbesserter Die-to-Wafer- Montageablauf öffnet Türen für Logik/Speicher-auf-Logik- Stacking und für Optisch vernetzte Systeme-auf-Wafer

Diese Woche präsentiert imec, ein weltweit führendes Forschungs- und Innovationszentrum für Nanoelektronik und digitale Technologien, auf der IEEE Electronic Components and Technology Conference (ECTC) 2024 einen Cu-zu-Cu- und SiCN-zu-SiCN-Die-to-Wafer-Bonding-Prozess, der zu einem Cu-Bondpad-Abstand von nur 2µm bei <350nm Die-to-Wafer- Overlay-Fehler führt und eine gute elektrische Ausbeute erzielt. Derartig feinkörnige Die-to-Wafer-Verbindungen ebnen den Weg für Logic/Memory-on-Logic- und Memory-on-Memory-Anwendungen. Längerfristig wird das Die-to-Wafer-Bonding auch optische Verbindungen auf Die- und Wafer-Ebene ermöglichen - wofür imec auf der ECTC2024 einen ersten Proof of Concept gezeigt hat.

Imec entwickelt einen Prozess für das direkte Die-to-Wafer-Hybrid-Bonden bei Interconnect-Pad-Abständen von deutlich unter 10µm, bis hinunter zu 1µm. Um diese Ziele zu erreichen, hat Imec seinen Prozess erheblich verbessert, insbesondere durch die Gewährleistung ultrareiner Oberflächen während der Verarbeitung, der Vereinzelung der Chips und der Bestückung sowie durch die Aufrechterhaltung eines hohen Durchsatzes während aller Prozessschritte. Dies hat zu einer ersten Demonstration mit einem Cu-Bondpad geführt, dessen Pitch auf nur 2µm skaliert.

Das Hybridbonden erfordert eine sehr hochwertige Oberflächenvorbereitung, um glatte Oberflächen mit einer minimalen Cu-Pad-Vertiefung (<2,5nm) zu erzielen, was eine sorgfältige Optimierung des chemisch-mechanischen Polierens (CMP) der Cu/SiCN-Oberfläche erfordert. Diese Eigenschaften müssen bei der Vereinzelung des Wafers und der Platzierung der Chips auf dem Wafer erhalten bleiben. Um eine qualitativ hochwertige Vereinzelung der Chips ohne Partikel und Auswirkungen auf die Cu/SiCN-Oberfläche zu erreichen, wurde ein Plasma-Dicing-Prozess eingeführt. Entscheidend für die Skalierung des Pad-Abstands ist ein schneller, aber hochpräziser Pick-and-Place-Schritt. Die Die-Verarbeitung zusammen mit einem hochpräzisen Pick-and-Place-Schritt führte zu <350nm Die-to-Wafer-Überlagerungsfehlern. Der Bestückungsablauf ermöglichte Cu-Bondpads im 2µm-Raster mit guter elektrischer Ausbeute: Kelvin e-yield >85% und Daisy Chain e-yield >70%.

Eric Beyne, Senior Fellow, VP of R&D und Program Director 3D System Integration bei imec sagte: "Was den Abstand der Verbindungen angeht, kann das Die-to-Wafer-Hybrid-Bonding jetzt die Lücke zwischen dem lötbasierten Die-to-Wafer-Bonding (das wahrscheinlich bei 10 bis 5µm Bump Pitch stagnieren wird) und dem Wafer-to-Wafer-Hybrid-Bonding (das Verbindungen deutlich unter 1µm ermöglicht, bis hinunter zu 400nm Pitch - wie von imec auf der IEDM 2023 vorgestellt - und möglicherweise bis 200nm Pitch in der Zukunft) schließen. Im Vergleich zu letzterem bietet das Die-to-Wafer-Bonding den Vorteil, dass nur bekannt gute Dies gestapelt werden (was zu einer höheren Ausbeute an Verbindungen führt) und dass Dies unterschiedlicher Größe verbunden werden können. Zukünftige Verbesserungen unseres Prozesses werden den Abstand der Verbindungen weiter in Richtung 1µm verschieben. Mit dieser Entwicklung kann das Die-to-Wafer-Bonding in den Bereich des Memory/Logic-on-Logic- und Memory-on-Memory-Stacking vordringen."

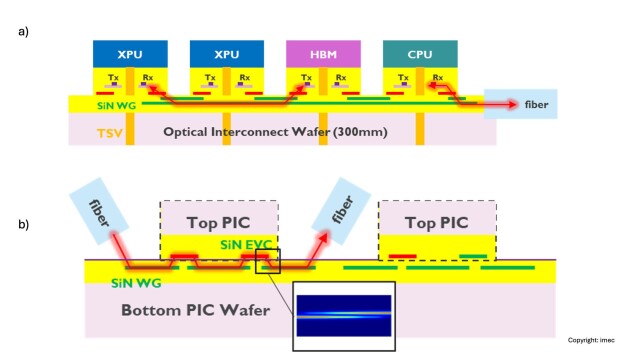

Darüber hinaus sind hochpräzise Die-to-Wafer-Bonding-Prozesse eine wichtige Voraussetzung für optische Verbindungen auf Waferebene - die langfristige Vision von imec für Verbindungen mit hoher Bandbreite und geringem Stromverbrauch zwischen mehreren Computerchips (xPUs) und Speicher mit hoher Bandbreite (HBM) in KI/ML-Clustern. Ein aus Kosten- und Ertragssicht attraktiver Ansatz ist die Aufteilung der optischen Verbindung in einen passiven optischen Verbindungswafer mit Long-Range-Routing-Wellenleitern und passiven optischen Funktionen und aktive photonische IC (PIC)-Dies (mit Modulatoren und Photodetektoren) - die wiederum mit einem elektrischen IC (XPU oder HBM) verbunden sind. Joris Van Campenhout, Fellow und F&E-Programmdirektor bei imec erläuterte: "Als erstes Proof-of-Concept haben wir eine verlustarme optische Kopplung zwischen PIC-Dies und einem 300-mm-Bottom-Wafer mit optischer Verbindung ermöglicht - unter Einsatz eines (kollektiven) SiCN-Dielektrikum-basierten Die-to-Wafer-Montageprozesses. Dank der präzisen Die-to-Wafer-Ausrichtung konnten niedrige optische Kopplungsverluste von unter 0,5 dB erzielt werden. In den nächsten Schritten werden wir unseren Montageablauf erweitern - z.B. indem wir auch Cu-zu-Cu-Verbindungen im gesamten Die-to-Wafer- Stack anbieten."

IMEC Belgium

3001 Leuven

Belgien