-

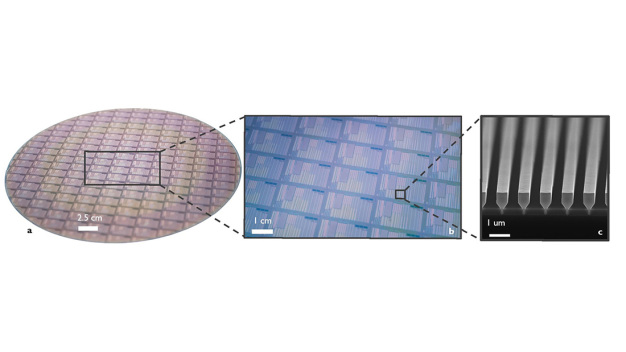

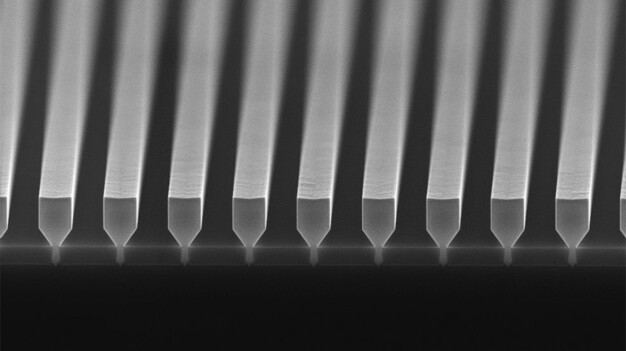

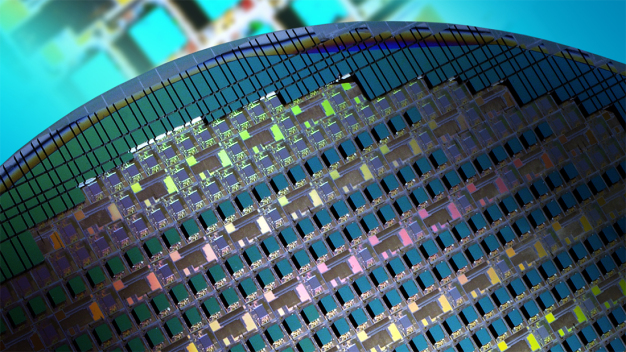

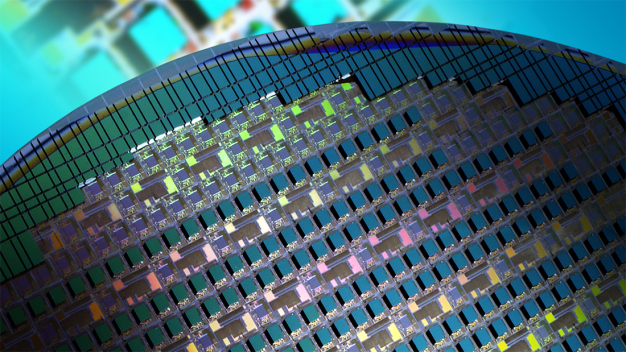

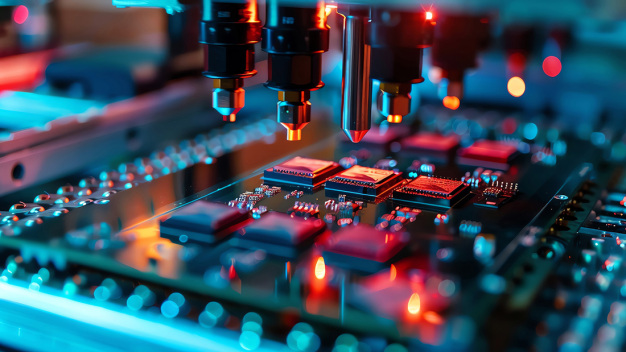

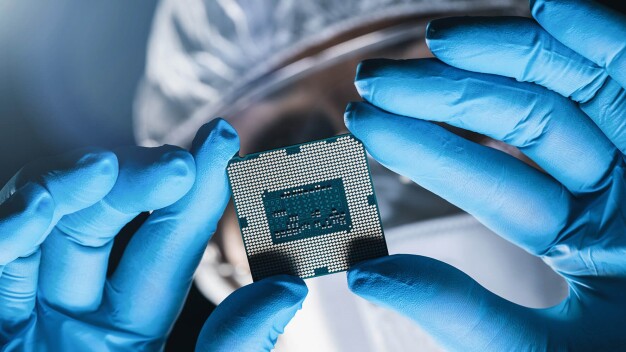

- Elektronik (Wafer, Halbleiter, Mikrochips,...)

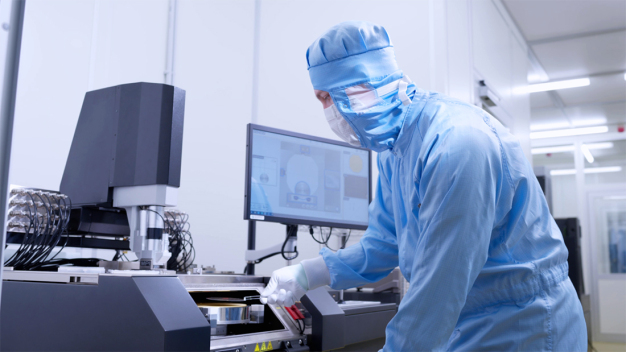

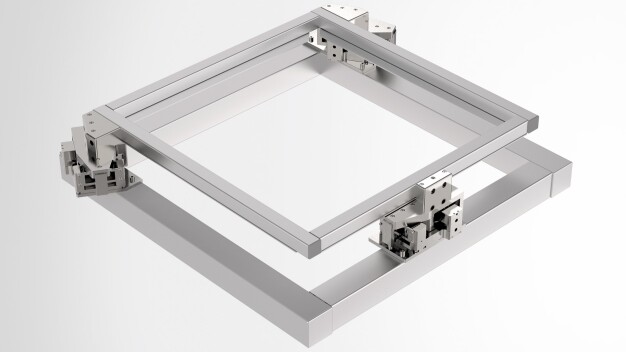

Reinraum zur Chip-Herstellung: Entscheidende Aspekte

Die Halbleiterfertigung ist auf Wachstumskurs. Wie realisiert man die dafür benötigten Reinräume am besten?

Ob Smartphones, Herzschrittmacher, Industrieroboter oder Alarmsysteme: Zahlreiche moderne Produkte sind auf Mikrochips angewiesen. Für die Gewährleistung eines fehlerfreien Betriebs erfolgt die…