-

- Wissenschaft

Neben Forschungsthemen standen insbesondere die Herausforderungen der angewandten Forschung und die Zusammenarbeit mit der Industrie im Mittelpunkt des Besuchs.

Wirtschaftsstaatssekretär Dr. Patrick Rapp besucht das Hahn-Schickard-Institut für Mikroaufbautechnik in Stuttgart

Die Institutsleiter Prof. Dr. André Zimmermann und Dr. Karl-Peter Fritz begrüßen Staatssekretär Dr. Patrick Rapp aus dem Ministerium für Wirtschaft, Arbeit und Tourismus Baden-Württemberg. Dr. Rapp traf sich mit wissenschaftlichen Mitarbeitern und Industriepartnern des Instituts zu einem Austa…

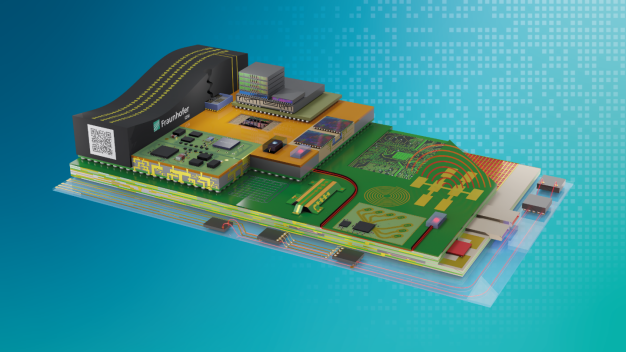

![Feierliche Übergabe des symbolischen Schecks über 38 Millionen Euro vom Ministerpräsident Michael Kretschmer an die sächsischen Mikroelektronik-Institute der Fraunhofer-Gesellschaft (v.l.n.r. Prof. Dr. Harald Kuhn [Fraunhofer ENAS], Prof. Dr. Martin Schneider-Ramelow [Fraunhofer IZM], Prof. Dr. Harald Schenk [Fraunhofer IPMS], Ministerpräsident Michael Kretschmer, Dr. Stephan Guttowski [Forschungsfabrik Mikroelektronik Deutschland], Prof. Dr. Peter Schneider [Fraunhofer IIS, Institutsteil Entwicklung Adaptiver Systeme], Dr. Oliver Höing [Bundesministerium für Bildung und Forschung BMBF]) © Fraunhofer IPMS Feierliche Übergabe des symbolischen Schecks über 38 Millionen Euro vom Ministerpräsident Michael Kretschmer an die sächsischen Mikroelektronik-Institute der Fraunhofer-Gesellschaft (v.l.n.r. Prof. Dr. Harald Kuhn [Fraunhofer ENAS], Prof. Dr. Martin Schneider-Ramelow [Fraunhofer IZM], Prof. Dr. Harald Schenk [Fraunhofer IPMS], Ministerpräsident Michael Kretschmer, Dr. Stephan Guttowski [Forschungsfabrik Mikroelektronik Deutschland], Prof. Dr. Peter Schneider [Fraunhofer IIS, Institutsteil Entwicklung Adaptiver Systeme], Dr. Oliver Höing [Bundesministerium für Bildung und Forschung BMBF]) © Fraunhofer IPMS](/uploads/images/_scale/mg8446apecsfoerderurkundempkretschmerfraunhoferipms_169_626x352.jpg)